Convertisseurs analogiques digitaux

et digitaux analogiques " un bit

" sigma delta.

I Convertisseurs AD " un bit ".

- Des livres à lire - Nouveau Livre ! - Liens et adresses -

Shanon - Contrôle prédictif - Lyapunov - DSP - Filtre RIF

Modes glissants - Conversion sigma-delta - Modulation AM - Commande avec frottement sec

Convertisseurs analogiques digitaux

et digitaux analogiques " un bit

" sigma delta.

I Convertisseurs AD " un bit ".

I.1 Présentation

Il est très difficile d'obtenir une conversion analogique digitale qui soit à la fois précise et rapide.

Les convertisseurs à double rampe et les convertisseurs à approximations successives sont précis, mais peu rapides.

Les convertisseurs flash (à comparaisons multiples directes) sont rapides, mais il est difficile d'ajuster les comparateurs internes de poids fort avec une précision de l'ordre de celle du bit de poids faible.

Les nouveaux moyens de communication requièrent pourtant des performances élevées, peu dispersées d'un composant à l'autre, dérivant peu dans le temps, et qui soient compatibles avec un coût raisonnable.

Ce coût dépend entre autres de la quantité de réglage en ligne de production. Il est aussi moindre lorsque le circuit intégré implémentant la fonction est seulement logique.

Aussi a-t-on développé des convertisseurs intégrant surtout des fonctions logiques, le traitement binaire du signal satisfaisant pratiquement à toutes les contraintes énoncées.

I.2 Principe du convertisseur " 1 bit " à haute fréquence ; modulateur sigma-delta.

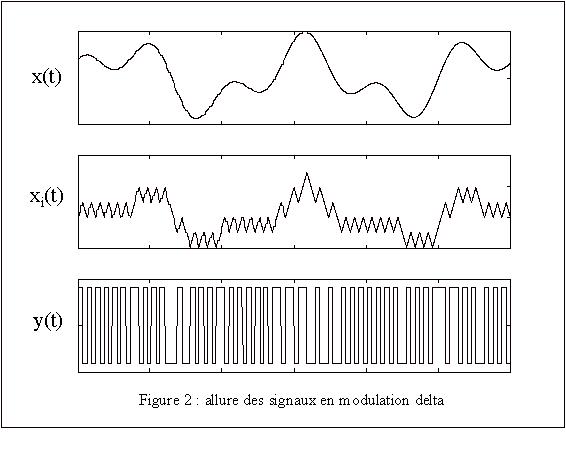

La méthode de conversion repose sur le principe de modulation dit " modulation delta". Il s'agit de coder, non pas le signal directement, mais l'écart entre deux échantillons successifs. Cet écart x(t) - xi(t) est codé sur un bit par un convertisseur très simple, composé d'un échantillonneur-bloqueur et d'un comparateur. Le signal y(t) à la sortie de ce dernier, bipolaire, représente l'augmentation ou la diminution du signal d'entrée sur un bit. Le signal d'entrée peut être reconstitué par simple intégration, et c'est ainsi que l'on obtient une image de l'échantillon précédent, xi(t). Le schéma de principe est donné figure 1 :

La fréquence d'échantillonnage fech 1 peut être très élevée, et même doit être très élevée pour obtenir un rapport signal/bruit acceptable. Ceci n'est pas en soi un handicap pour le domaine des communications audio, car on peut sans peine fabriquer des circuits fonctionnant à fech 1 = quelques Mhz. L'intégrateur peut être de très bonne qualité, par exemple à capacités commutées.

La figure 2 illustre le principe de la modulation delta (pour une fréquence d'échantillonnage faible).

Le même modulateur peut être réalisé avec une intégrateur échantillonné synchrone de l'horloge de la chaine directe. On obtient alors les signaux suivants (figure 3) :

On notera en outre que le fait d'échantillonner largement au-dessus de la fréquence de Nyquist du signal permet d'alléger les contraintes sur le filtre anti-repliement, ce qui facilite sa réalisation. Le bruit de quantification est pour sa part étalé sur un spectre plus large, ce qui diminue sa densité spectrale de puissance.

Le modulateur delta (codage de la variation) associé à la boucle de réaction (comparateur de retour = additionneur = sigma) porte le nom de modulateur "sigma-delta".

I.3 La démodulation

Cette opération très simple, déjà vue en I.2), consiste simplement à intégrer le signal y(t), avec éventuellement un filtrage passe-bas en sortie. Ce filtre est aisément implanté à l'aide d'un réseau à capacités commutées.

I.4 Obtention d'un code sur n bits

La sortie y(t) peut être convertie en une sortie z(t) codée sur n bits à une fréquence plus faible fech 2. Cette opération, dite de décimation-filtrage, consiste à ne conserver qu'un nombre restreint d'échantillons, après filtrage numérique.

Une méthode très simple consiste à effectuer la moyenne de n valeurs de y(t), prises à la fréquence fech 1 , pour créer un échantillon de z(t). On aura donc fech 2 = fech 1 / n .

Cette moyenne peut prendre 2n valeurs, et le filtre numérique qui la calcule fournira donc une sortie sur n bits.

On a donc réalisé de la sorte un convertisseur AD comportant essentiellement des éléments binaires.

On peut rencontrer d'autres structures reposant sur le même principe, différant essentiellement par la place de l'intégrateur dans la boucle.

I.5 Limitations

Saturation de la pente : si on appelle d l'amplitude de la sortie du comparateur et T la période d'échantillonnage, alors la pente maximale du signal de poursuite est d / T ; un signal de pente supérieure ne peut être poursuivi et une distorsion apparaît :

Figure 4 : saturation de la pente du convertisseur

Sous échantillonnage : si la condition de fréquence de Nyquist n'est pas respectée, la conversion est affectée d'aliasing :

Figure 5 : fréquence d'échantillonnage trop faible

Granularité : si d est trop fort, le signal démodulé est très découpé, et le rapport signal/bruit se détériore (cet effet est analogue à celui qu'on obtient avec un ADC utilisé sur une trop petite gamme d'entrée) :

Figure 6 : détérioration du rapport S/B dû à trop de granularité.

I.6 Convertisseur adaptatif : les systèmes évolués adaptent en temps réel les paramètres de conversion en fonction d'un critère de qualité. Il est ainsi possible d'obtenir des performances régulières sur des signaux présentant un large spectre et une dynamique élevée (c'est le cas par exemple du signal de parole). L'étude des mécanismes d'adaptation sort du cadre de cet exposé, mais les principes directeurs sont les mêmes que ceux des régulateurs d'asservissement adaptatifs.

II Convertisseurs digitaux analogiques " un bit ".

II.1 Présentation

Les convertisseurs digitaux analogiques habituellement rencontrés reposent sur le principe de l'échelle résistive ( ou, ce qui revient au même, sur une batterie de comparateurs), et même s'ils ne présentent pas la lenteur qui caractérise les convertisseurs AD ( le moindre CDA convertit en 100 ns ! ), ils sont soumis aux mêmes limitations en précision, dérive, ajustage, etc... On a donc intérêt à procéder d'une manière similaire à ce qui vient d'être montré : troquer un grand nombre de bits à faible cadence contre un petit nombre à haut débit.

II.2 Convertisseurs DA multicadences ( multirate bit-stream DACs )

La première étape est très similaire à celle étudiée dans la section I . Le schéma de principe en est donné figure 7 : une entrée numérique codée sur n bits, à la fréquence fech 2 est comparée à l'entrée précédente, et le résultat est quantifié sur un bit. La boucle procède à la fréquence fech 1 = n x fech 2 .

II.2 Conversion analogique : sortie analogique

La sortie à haute fréquence sur un bit peut être dénommée "modulation de densité d'impulsions" ( voir les figures de la section I ), MDI. Elle peut aussi être codée sous forme de MLI (modulation de largeur d'impulsions) dans certains circuits.

Dans le cas de la MDI, le convertisseur de sortie proprement dit est réalisé à l'aide d'un filtre à capacités commutées suivi d'un simple filtre passe-bas.

II.3 Suréchantillonnage de sortie

Les principes évoqués précédemment bénéficient des progrès constants sur la rapidité des circuits : les fréquences de traitement atteignent facilement quelques dizaines de Mhz.

Aussi, il n'est pas rare de rencontrer des circuits qui poussent à leur maximum les concepts d'échantillonnage rapide. L'exemple qui suit concerne les technologies du son.

L'entrée sur n bits est souvent convertie numériquement sur n+m bits ( la fréquence étant alors multipliée par m ) par un filtre interpolateur (numérique).

Puis, un filtrage numérique passe-bas, à fréquence de coupure 22 kHz, opère une réduction de la bande passante qui facilitera la conversion.

Celle-ci est soit du type direct ( jusqu'à 18 bits de résolution), soit du type bit-stream, cette dernière option étant la plus courante actuellement.

II.4 Généralisation

Le principe d'intégration utilisé jusqu'à présent peut être généralisé à des intégrateurs multiples. On a alors affaire à des modulateurs sigma delta d'ordre supérieur à un.

Nous ne les détaillons pas ici.

Pour des exemples, voir chez Texas Instruments, par exemple.

Revenir à la page d'accueil

Revenir à la page Concours

- Des livres à lire - Nouveau Livre ! - Liens et adresses -

Shanon - Contrôle prédictif - Lyapunov - DSP - Filtre RIF

Modes glissants - Conversion sigma-delta - Modulation AM - Commande avec frottement sec