|

|

|

|

|

|

|

5.1 Fonction dusage:

Le pageur est utilisé afin de recevoir des informations sur un afficheur à cristaux liquides, par le biais des ondes radio dans la bande FM (88 à 108 Mhz).Le pageur est de petite taille et se place facilement dans une poche.

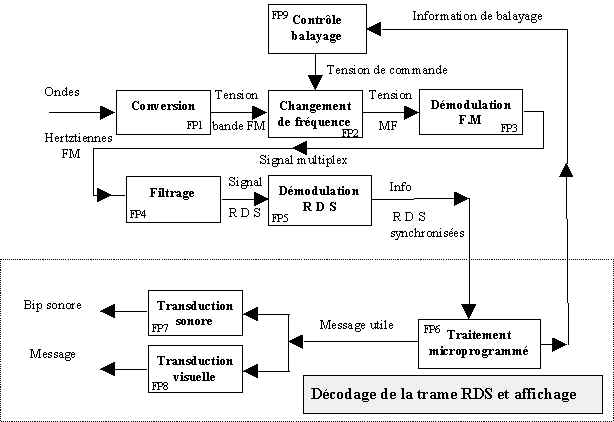

5.2 Shéma Fonctionnel du Pageur:

5.3 Shéma Fonctionnel de degré 1 du Pageur:

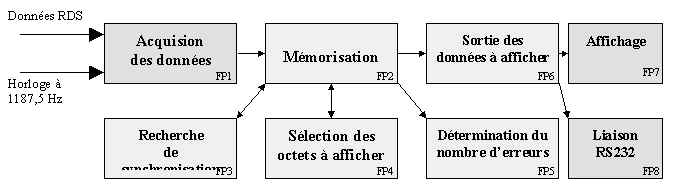

3.2 Shéma Fonctionnel de degré 1:

4) Décodage de la Trame RDS et Affichage

* FP1 Acquisition des données

Fs11: cette fonction fait une acquisition de 26 bits sous forme série .Lacquisition se fait sur front montant du signal dhorloge ( la fréquence de cette horloge étant de 1187,5 Hz ).

Les bits reçus sont mémorisés temporairement dans laccumulateur A .

Fs12: cette fonction convertit les 26 bits recus sous forme série en quatre octets dont un ne possède que 2 bits : b0,b1 .Un octet est formé à partir de 8 bits qui sont décalés un à un.Un octet est donc convertit au bout de 8 coups dhorloge.Les deux derniers bits sont aussi convertis sous 8 bits mais les 6 autres bits sont à 0 .

* FP2 Mémorisation

Fs21: cette fonction mémorise les 4 octets en ram afin de pouvoir les utiliser ultérieurement .

Fs22: cette fonction mémorise les 4 blocs en ram afin de pouvoir exploiter les données reçues.

* FP3 Recherche de la synchronisation

Fs31: cette fonction utilise les quatres octets mis en mémoire et calcule leffet en multipliant les 26 bits reçus par la matrice H.

Fs32: cette fonction compare leffet calculé sur 2 octets aux cinq effets connus.Si un des cinq effet est trouvé, cest que lon a reçu un des cinq bloc.Pour des raisons defacilité, on compare leffet trouvé à celui du bloc 1, de manière à sy retrouver plus facilement dans les données à extraire.

Fs33: cette fonction fait lacquisition dun 27ème bits sur front montant de lhorloge et décale tous les bits afin de nen conserver que 26.

* FP4 Sélection des octets info à afficher

Fs40: cette fonction permet de sélectionner le bloc choisi afin de décoder par exemple: le code PI dans le bloc1, le code PS dans les blocs 3 et 4 ...

Cette fonction permet aussi de choisir le type de groupe recherché. Le type de groupe est choisi à laide des micro-switchs implantés sur la carte.

* FP5 Contrôle des erreurs

Fs50: cette fonction permet à partir de leffet de vérifier si la trame comporte des erreurs ou non.Il est possible grâce au mot de contrôle et à leffet de corriger des erreurs si il ny en a pas trop. Cette fonction permet ainsi de compter le nombre derreurs reçues.

* FP6 Sortie des données à afficher

Fs60: cette fonction envoie sur le port B la donnée à afficher sur lafficheur.La donnée est codée sur 8 bits.

*FP7 Affichage

Fs70: cette fonction affiche directement sur lafficheur LCD linformation voulue provenant du signal RDS décodé.Il sera possible dafficher diverses informations telles que le code PI , Le code PS ...

Fs71: Cette fonction permet denvoyer à un micro-ordinateur les données RDS sélectionnées par la fonction FP4, afin de pouvoir les traiter et même de les mémoriser de façon logicielle ( Turbo pascal , Turbo C++ ... ).

5) LES DIFFERENTES

SOLUTIONS ENVISAGEES

Introduction:

La tâche Décodage des données RDS et affichage est en majeur partie, une tâche réalisée de façon logiciel. La carte réalisée de façon matérielle ne comporte, quun microcontrôleur de type 68HC811E2 et dune interface série, réalisée à laide dun composant courant: le MAX 232.

Sur le plan matériel:

Sur le plan matériel, une amélioration a été effectuée par rapport au cahier des charges initial. A létat initial, seul laffichage sur un écran à cristaux liquides était prévu; comme le microcontrôleur devait fonctionner en mode fermé, la réalisation matérielle ne nécessitait que le microcontrôleur, lui même et lafficheur LCD ( sans tenir compte du Quartz et de quelques composants passifs ). Lamélioration proposée a été dintroduire sur la carte, une interface série, afin de pouvoir communiquer avec le 68HC811E2. A laide de linterfaçe, il serait ainsi possible de recevoir des données RDS sur un ordinateur et ainsi de pouvoir les traiter de façon logiciel. Il serait aussi possible dindiquer au microcontrôleur quel groupe doit-il filtrer et envoyer sur linterfaçe série.

Sur le plan logiciel:

Au niveau logiciel, une modification a été effectuée au tout début du projet car le sous programme traitant le calcul de leffet ( cf calcul de leffet ), prenait trop de temps: le temps de calcul maximum entre 2 bits de données RDS est de 842 uS. Des mesures ont été faites et on montré que le programme chargé du calcul de leffet nécessitait plus de 842 uS. Une fois le calcul terminé, le système étant synchronisé ou non, le temps excessif de calcul provoquait la perte dune donnée RDS. Même si le système était synchronisé, la perte dune donnée a faussé toute la suite des opérations ce qui provoque ainsi la perte de synchronisation.

Le problème quil fallait donc résoudre au niveau logiciel était de modifier le programme afin de diminuer ce temps de calcul ( temps souhaité inférieur à 842 uS ).

Une fois le programme modifié, plus de données ne seraient perdues et le système resterait synchronisé une fois quun effet corresponderait à un des 5 connus.

Relevé du temps mis pour calculer leffet:

Pour relevé le temps mis, jai réalisé un programme qui ne faisait que le calcul de leffet et à l'aide de celui-ci, jai mesuré le temps mis pour calculer celui-ci au fréquencemètre. Jai effectué la vérification de cette mesure en calculant le nombre de cycles mis pour effectuer le programme. Les deux mesures se sont rejoints et on montrées que le programme mettait environ 5,05 ms pour calculer leffet. Le temps mis ici, était beaucoup trop élevé et jai pu le diminuer suffisamment en modifiant toute la structure du programme ( changer complètement la méthode de multiplication par la matrice H ).

9) CARTE MEMOIRE

Introduction: le programme réalisé utilise la RAM interne du 68HC811E2 pour effectuer la mémorisation des données RDS et des données qui seront affichées sur lécran LCD ou qui seront envoyées sur linterface serie.

Fcarte mémoire :

7) LA MATRICE H

Introduction: la matrice H permet dune part, de savoir si le système est synchronisé ou non et dautre part de détecter si une erreur est intervenue.Dans le cas de mon projet, jutilise cette matrice afin de me synchroniser avec les données. Pour ce, il faut multiplier les 26 bits de données mis en mémoire, par cette matrice. Une fois la multiplication effectuée, il ne reste plus quà comparer le résultat avec les 5 effets connus ( voir les différents effets ). Si un des 5 effets est reconnu, cela signifie que le système est synchronisé sur le bloc correspondant à cet effet. Pour des raisons de simplicité, je considérerai que le système sera synchronisé une fois que jaurai reçu leffet correspondant au bloc 1 : $F6.

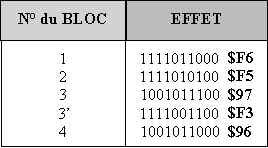

Les différents effets:

Matrice de contrôle de parité H:

1 0 0 0 0 0 0 0 0 0

0 1 0 0 0 0 0 0 0 0

0 0 1 0 0 0 0 0 0 0

0 0 0 1 0 0 0 0 0 0

0 0 0 0 1 0 0 0 0 0

0 0 0 0 0 1 0 0 0 0

0 0 0 0 0 0 1 0 0 0

0 0 0 0 0 0 0 1 0 0

0 0 0 0 0 0 0 0 1 0

0 0 0 0 0 0 0 0 0 1

1 0 1 1 0 1 1 1 0 0

0 1 0 1 1 0 1 1 1 0

0 0 1 0 1 1 0 1 1 1

1 0 1 0 0 0 0 1 1 1

1 1 1 0 0 1 1 1 1 1

1 1 0 0 0 1 0 0 1 1

1 1 0 1 0 1 0 1 0 1

1 1 0 1 1 1 0 1 1 0

0 1 1 0 1 1 1 0 1 1

1 0 0 0 0 0 0 0 0 1

1 1 1 1 0 1 1 1 0 0

0 1 1 1 1 0 1 1 1 0

0 0 1 1 1 1 0 1 1 1

1 0 1 0 1 0 0 1 1 1

1 1 1 0 0 0 1 1 1 1

1 1 0 0 0 1 1 0 1 1

Principe pour multiplier les 4 octets par la matrice H :

Les 26 bits mémorisés sont convertis sous formes de 3 octets entier et dun quatrième octet ne comportant que les deux derniers bits de donnée. Le principe pour multiplier ces 26 bits par la matrice est de prendre le premier bit reçu et de stocker en mémoire la première ligne de la matrice si la premier bit reçu est à 1; Au cas contraire il faut remplacer la ligne de la matrice par $0000 et de stocker cette valeur en mémoire.Ensuite, toujours sur le même principe, on teste létat du deuxième bit reçu et on stocke en mémoire $0000 si ce bit est à 0, ou alors la deuxième ligne de la matrice. On garde le même principe pour les 26 bits et une fois les 26 bits testés, on fait un ou exclusif entre les 26 adresses paires de la matrice pour obtenir le résultat de la multiplication; Dans ce cas, on obtient le MSB. Pour obtenir le LSB, on fait un ou exclusif avec les 26 adresses impaires de la matrice. On obtient donc le résultat sous 16 bits et lon vient enfin de calculer leffet. Il ne reste plus quà comparer leffet reçu aux 5 effets connus. Daprès ces 5 effets, le LSB provenant du calcul doit être à $00 dans tous les cas. Cela simplifie très nettement la comparaison et il ne reste plus quà tester le MSB. Celui-ci doit être égal à $F6 pour être synchronisé sur le Bloc 1.

Remarque :

Les 26 bits de données sont convertis sous forme de quatre octets, pour tester les 26 bits un à un, il faut décaler loctet vers la gauche et tester létat de la carry; la carry représente ainsi létat du bit à tester. Une fois que loctet a été décalé 8 fois, on change doctet et ainsi de suite. Il ne reste plus quune petite subtilité pour le quatrième octet; en effet, les 3 premiers octets on été décalés vers la gauche mais pour des raisons de simplicité, le dernier octet sera décalé vers la droite puisquil ne contient que les deux bits de poids faible ( on fera attention à ne pas oublier dinverser les deux dernières lignes de la matrice car le 26ème bit sera testé avant le 25ème ).

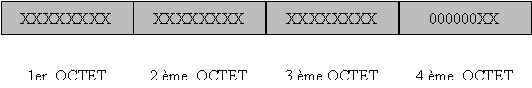

Constitution dun bloc de 26 bits :

F On peut remarquer

que le quatrième octet ne contient que deux bits de poids faible.