Calcul capacité , écriture des équations de sortie

et recherche du schéma structurel .

Caractéristiques du système étudié :

-

un bus d'adresses de 16 bits (A15....A0)

-

un bus de données de 8 bits (D7....D0)

-

la mémoire ROM est située de A000 à BFFF

-

la mémoire RAM est située de 6000 à 7FFF

Aprés étude les équations logiques pour le décodage

d'adresses sont :

-

CS\RAM = (A15\ . A14 . A13)\

-

CS\ROM = (A15 . A14\ . A13)\

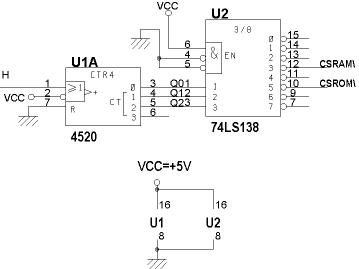

Schéma structurel :

Générer les signaux en fonction du temps (séquentiel).

Il fournit toutes les combinaisons possibles pour le décodeur

74LS138.

Voir test en dynamique

Câblage et tests en statique :

Les états sur les entrées sont fixées par des fils

de câblage.

Les différentes mesures sont effectuées avec un voltmètre

continu.

Tableau de mesures relevé :

Conditions : Vcc= 5 Volts

Toutes les mesures sont en volts.

| A15 |

A14 |

A13 |

Y0\ |

Y1\ |

Y2\ |

Y3\ |

Y4\ |

Y5\ |

Y6\ |

Y7\ |

| 0 |

0 |

0 |

0 |

5 |

5 |

5 |

5 |

5 |

5 |

5 |

| 0 |

0 |

5 |

5 |

0 |

5 |

5 |

5 |

5 |

5 |

5 |

| 0 |

5 |

0 |

5 |

5 |

0 |

5 |

5 |

5 |

5 |

5 |

| 0 |

5 |

5 |

5 |

5 |

5 |

0 |

5 |

5 |

5 |

5 |

| 5 |

0 |

0 |

5 |

5 |

5 |

5 |

0 |

5 |

5 |

5 |

| 5 |

0 |

5 |

5 |

5 |

5 |

5 |

5 |

0 |

5 |

5 |

| 5 |

5 |

0 |

5 |

5 |

5 |

5 |

5 |

5 |

0 |

5 |

| 5 |

5 |

5 |

5 |

5 |

5 |

5 |

5 |

5 |

5 |

0 |

Voir cours décodage d'adresses

Câblage et tests en dynamique avec un compteur 4520

:

Voir schéma çi dessus

Il est fourni par un GBF réglé à 10kHz avec un signal

carré d'amplitude 0/+5V, car le 74138 est un circuit en technologie

TTL.